## System On a Programmable Chip (SOPC) based Power Electronic Controller

By

AJEESH A CDAC-Thiruvananthapuram ajeesh@cdac.in

CDAC(T)

C-DAC ©All Rights Reserved

# **Some Calculations**

### A Processor with one million switching devices

### Use Vacuum tubes (Triodes) ,not MOS Transistors

C-DAC @All Rights Reserved

Area

Assume the triode occupies an area of 5cm X 5cm including some space between adjacent tubes

## $\Box$ Total area of 50 X 50 =2500 m<sup>2</sup>

$\Box$  With multilayer area = 22m X 22 m

## **Power consumption**

#### Assume

## □Taking 5W per triode

### □Half of the triodes are conducting at any time

# The total power consumed = $0.5 \times 10^6 \times 5$ = 2.5 MW

# **Heat dissipation**

## **Heat dissipation**

# Reliability

## Let 'T' – Life of a transistor in hours

## ≻ Replace

on an average one triode every  $T/10^6$  hr

Grant T =

$$10^6$$

Then we need to replace a triode every

"one hour"

24X7 maintenance

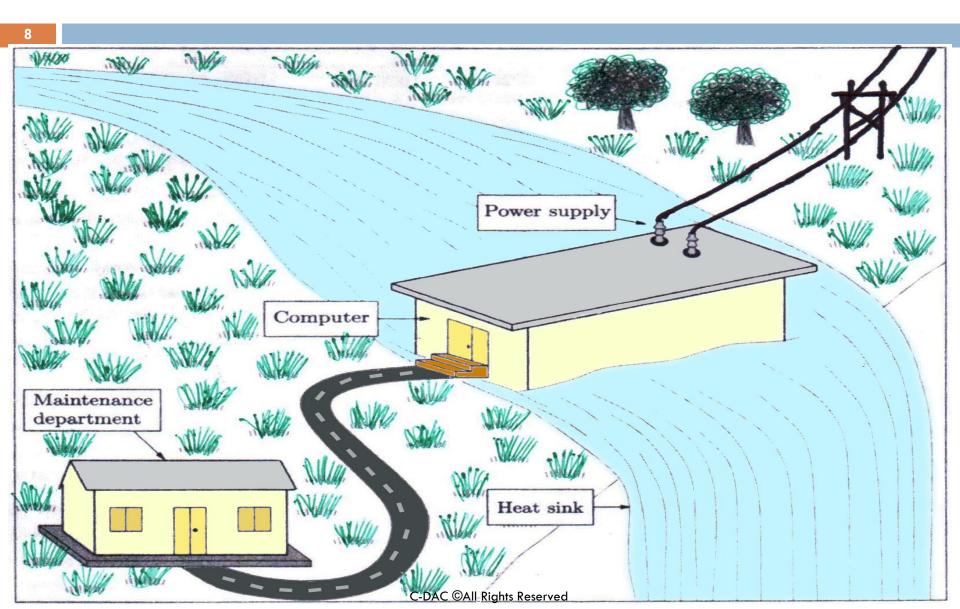

# The system

Speed

## Below 1 MHz due to parasitic wiring capacitance and Inductance

### Longer development time

C-DAC ©All Rights Reserved

# Area/Size Power Consumption Reliability Speed Time to market

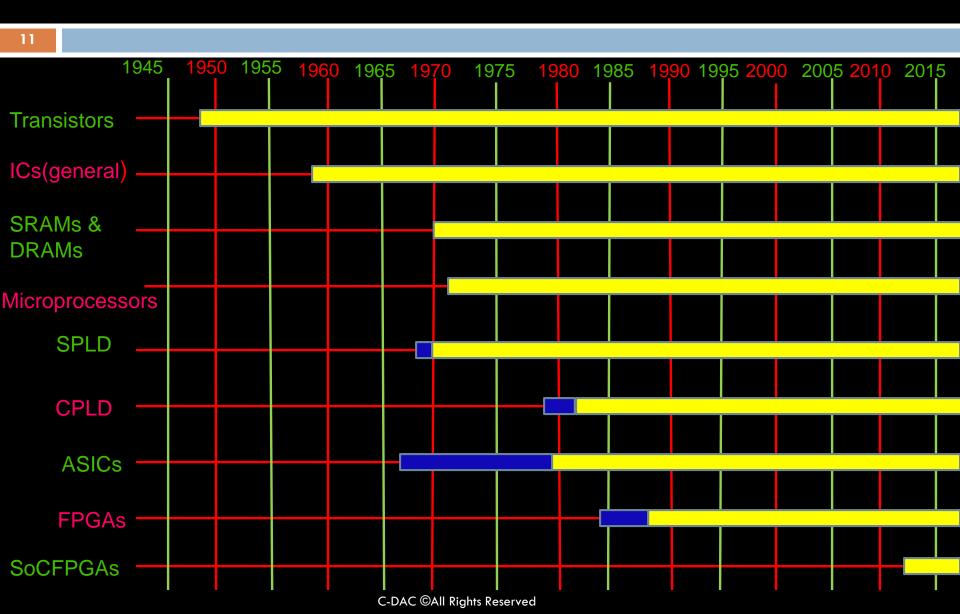

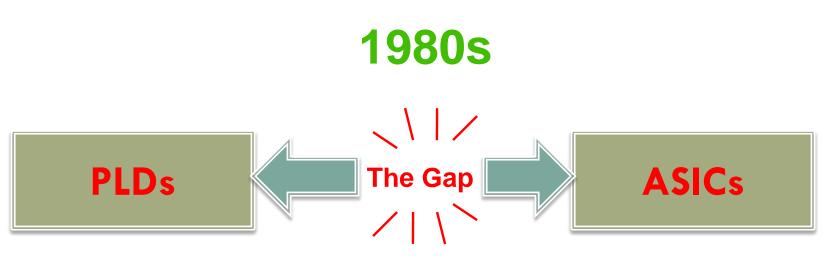

# Programmable chip

>configurable

Fast design and modification timeCould not support large or complex

functions

support large or complex functions Expensive and Time consuming ▶Frozen in Silicon

Highly configurable

Fast design and modification time

Could not support large or complex functions

support large or complex functions

Expensive and Time consuming

Frozen in Silicon

#### Xilinx Introduced FPGAs in Market CMOS – SRAM Based

19

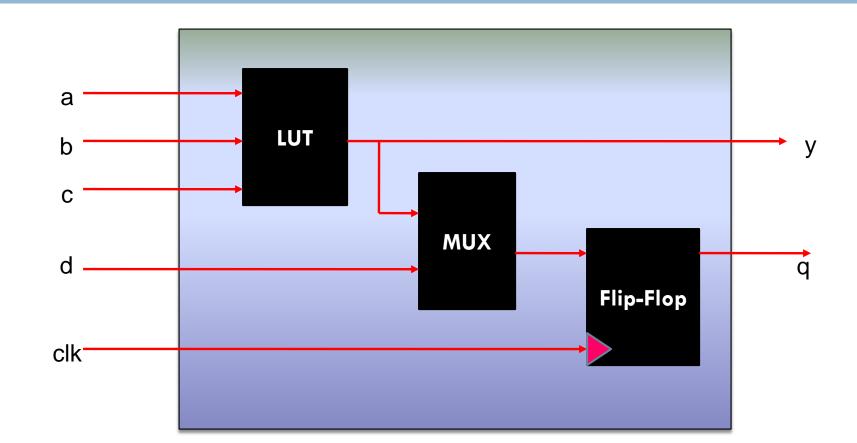

### Programmable logic Blocks

- A 3 input Lookup table (LUT)

- Flip-Flop or Latch

- > A Multiplexer

## Modern FPGAs Contains complex versions of "Programmable logic Blocks"

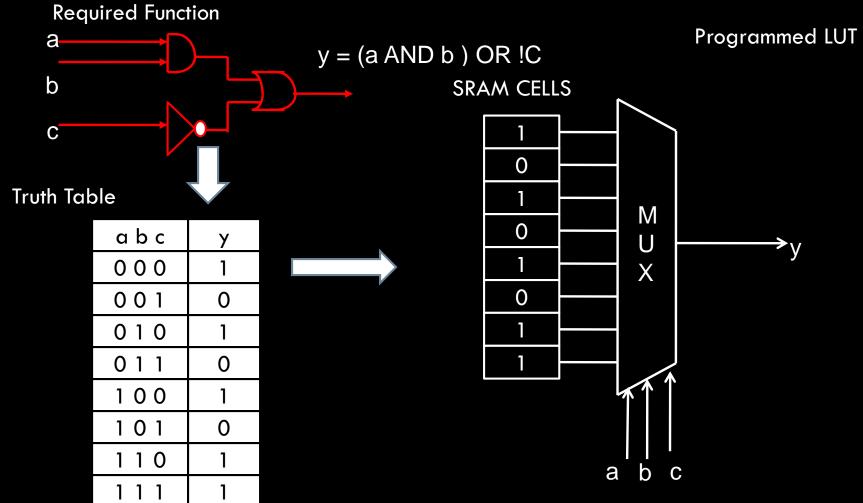

Using SRAM every logic block in the device can be programmed

20

C-DAC @All Rights Reserved

# **Configuring LUT**

21

C-DAC ©All Rights Reserved

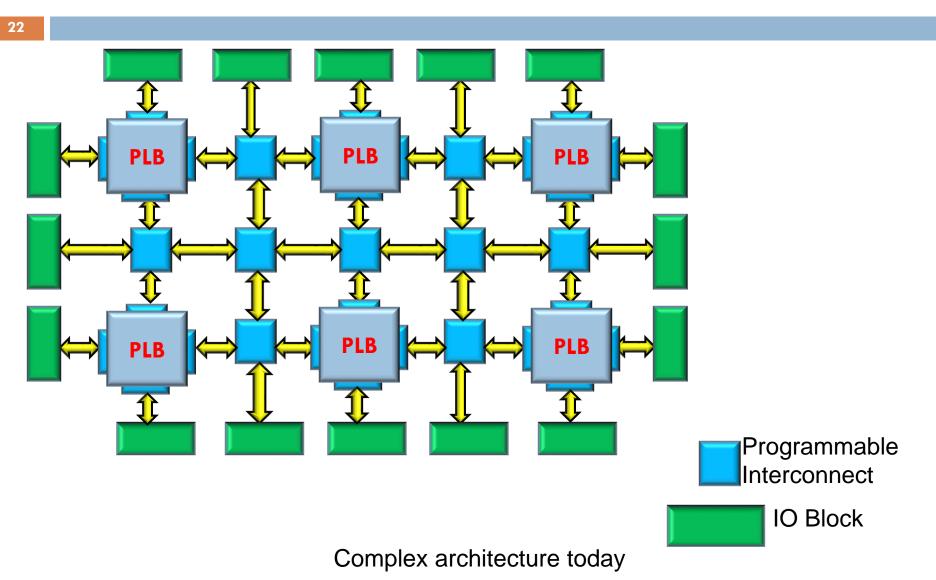

# **FPGA** Structure

C-DAC @All Rights Reserved

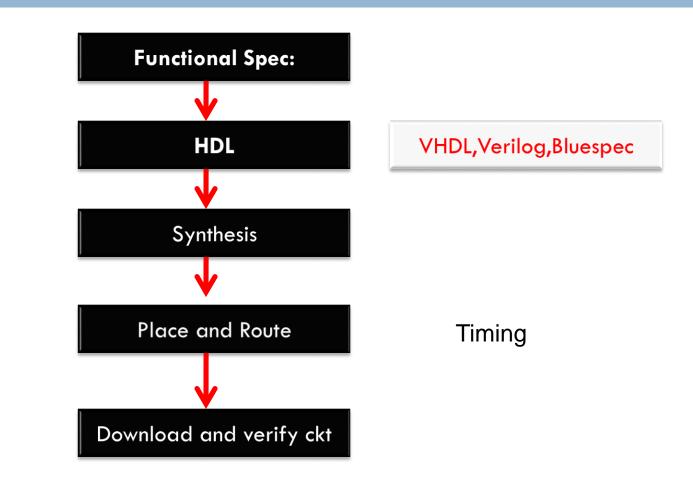

# **FPGA Design Flow**

# **PE Control System Design**

### □ Analog – Using OP-AMPS, Resistors, Capacitors etc.

#### Digital – Using Processors and software programming

Logics and numerical methods – DSPs

# "What if have a Processor so that user defines Instructions, Internal Modules, Speed, Memory, pins etc. ???" Obsolescence free design!!!

26

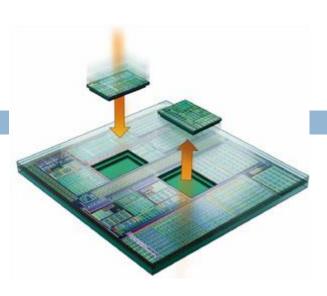

- "Building embedded system into a single programmable integrated circuit like FPGAs"

- Generally involves utilization of a large FPGA

- > Processor cores (Soft / Hard)

- Memory(RAM and ROM)

- Intellectual property (IP) ,Custom hardware blocks/IPs

*"have all (or majority) of the components on a single programmable chip"*

## **Need for Development**

#### **SOPC PE Controller**

Long term support for Hardware and software

Industrial PE systems, Power system controls etc. (5 -10Y)

**Railways, Defense Application (10-30Y)**

- Processor Obsolescence in 4 6 years

- Next generation Processor : Software porting overhead according to Processor Hardware changes

soft processor IP core in general purpose FPGA

Single chip Solution:

Difficult to find a processor with all interfaces/reconfigurable for the application

Custom made IPs with the CPU core

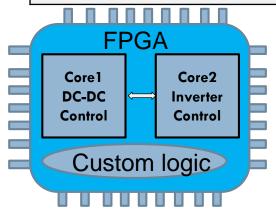

Single core to multi core : with increased cost, may require hardware redesign

same FPGA Hardware for single to multi core application

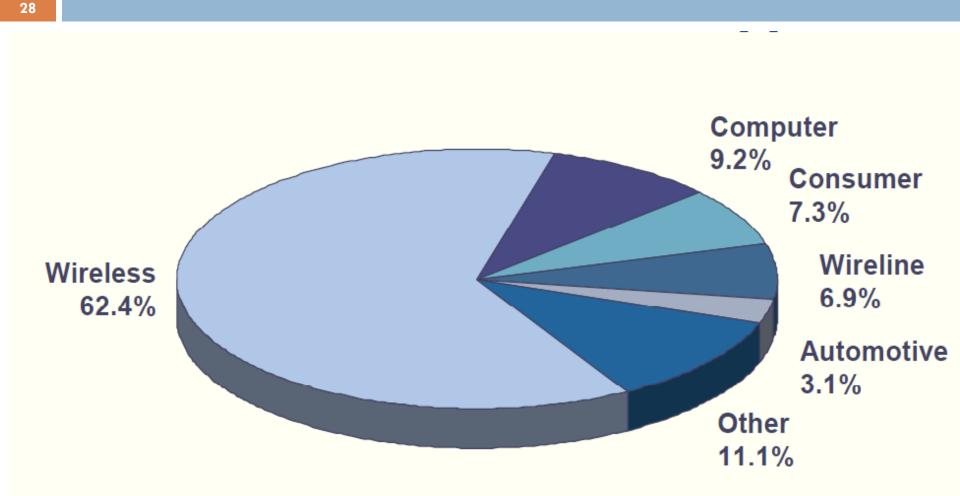

# Need for Development DSP Revenue

Nobody is going to use a mobile more than 20 Years

# **Need for Development**

29

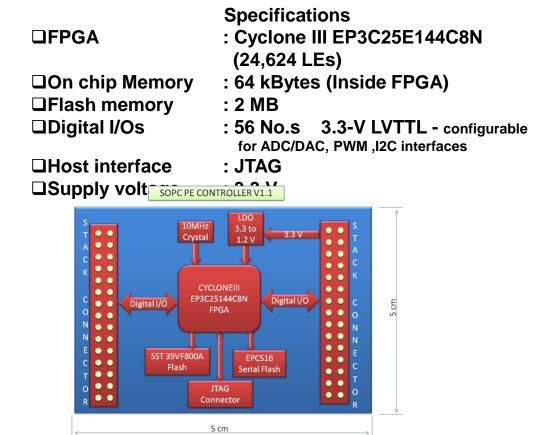

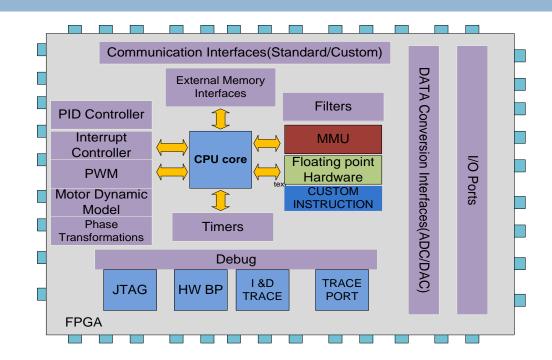

#### Faster Controller : Sampling of 5 -10 microsec or less

- Use Parallel processing multi-core processor integration

- Use Hardware accelerators Control blocks in dedicated hardware to perform functions faster than a CPU (PI, Filters, PLL, PWM)

- C2H Compilers: Inspect the application 'C' code and try to convert time consuming software algorithms into equivalent hardware implementation

Hardware performs faster than software

- Hardware Parallel Processing than Software pipelining

8201 NIOS II cycles equivalent to 24603 TigerSHARC cycles

(200 MHz vs 600 MHz)

Better Time to Market criteria

- Same FPGA Board

- Description Proven CPU and IP core Set

#### handles a wide range of applications

# **Need for Development**

#### Higher reliability

Higher level of integration and resources utilization of a single FPGA

#### <u>Board Design</u>

On chip interconnections : Industry standard (AVALON, AMBA AXI ) Internal PLLs : Remove the need to distribute high speed clocks round a PCB Reduced EMI

"PCB can be smaller, consume less power, be easier to get through EMC tests"

#### **Board Testing**

"Dedicated test designs can be loaded into the FPGA to automate Board testing"

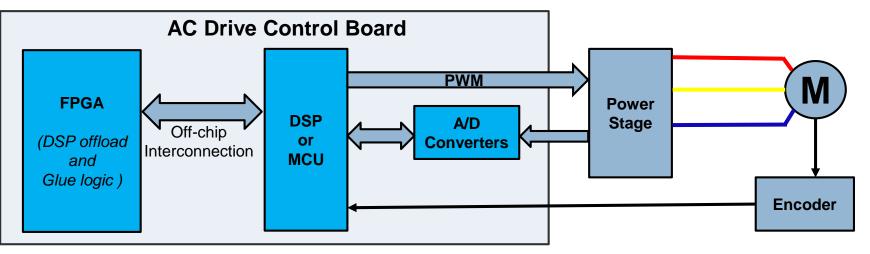

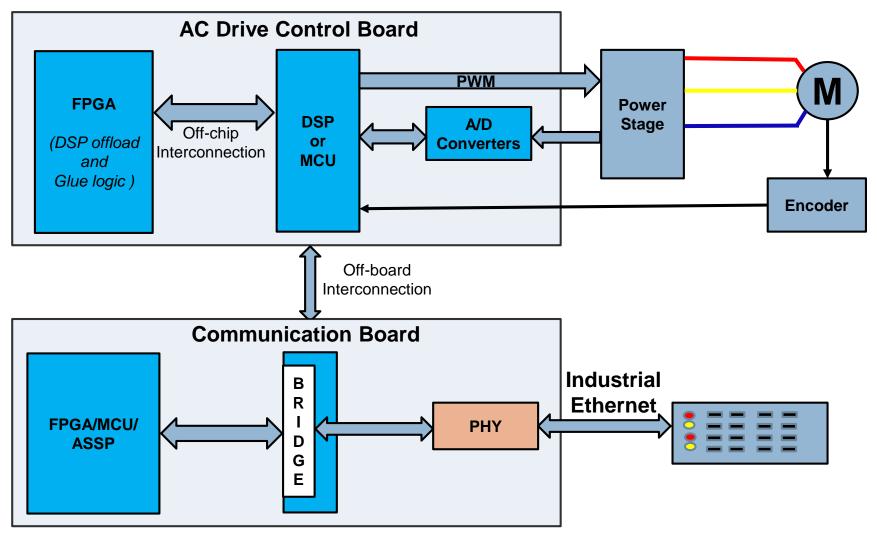

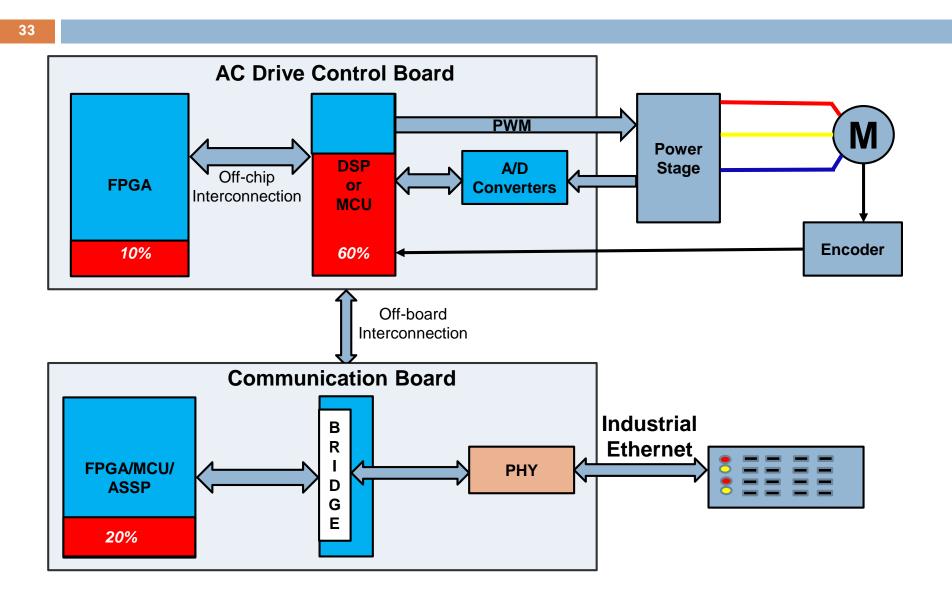

#### **31 CONVENTIONAL CONTROLLERS**

#### **32 CONVENTIONAL CONTROLLERS**

# **Resource Utilization**

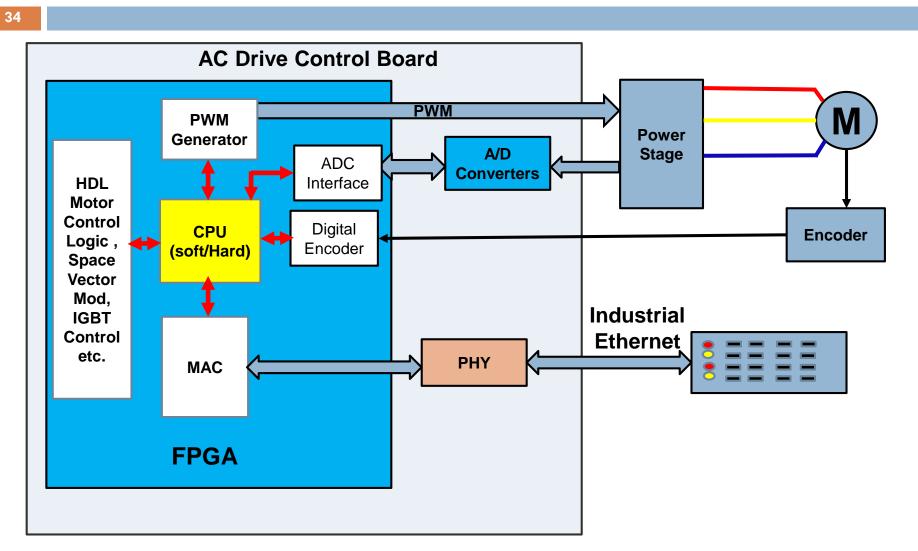

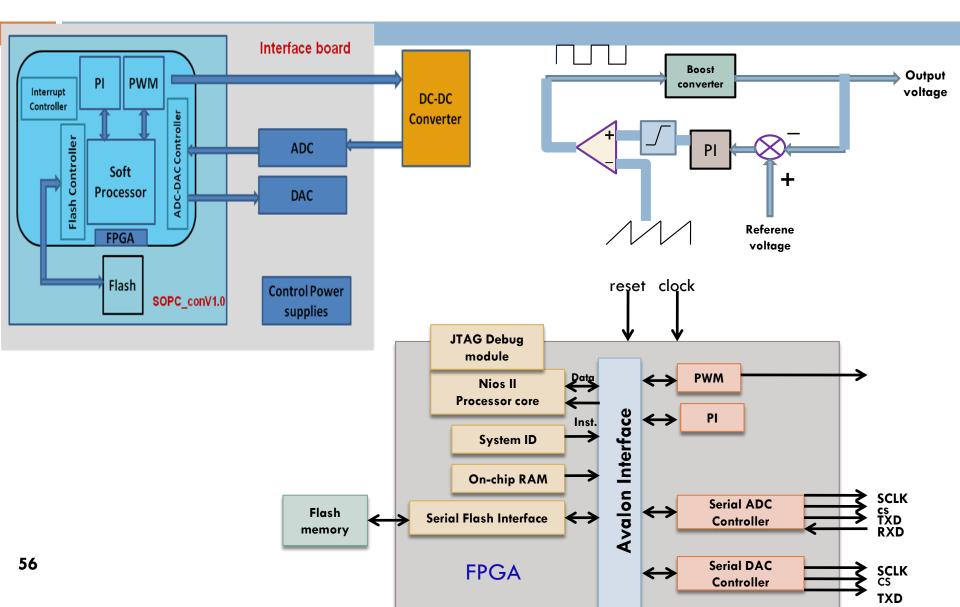

# **SOPC PE Controller**

**FPGA** as a Drive Controller Chip

35

**MPF**

□ This Generic Board can handle Most of the PE applications

□ The Hardware inside the FPGA is Configurable depending on PE Application

□ The I/Os are Configurable

# **Peripheral Interface Card**

#### SOPC INTERFACE CARD

#### **Targeted Application**

- DC-DC converter control

- •AC drive applications

- •Front end converter etc.

#### □ Specifications

- ≻Analog Input

- ➢Analog Output

- ➢Digital input

- ➢Digital Output

- : +10V (ADC 13 bit 8 Channel, SPI interface)

- : +3.3V (DAC 12 bit 8 Channel, SPI interface)

- : +5V

- : +5V

- ≻Supply voltage : 24 V

Stack Connector for SOPC\_CONTROLLER Card "CUSTOM DESIGN FOR SPECIFIC APPLICATION IS POSSIBLE"

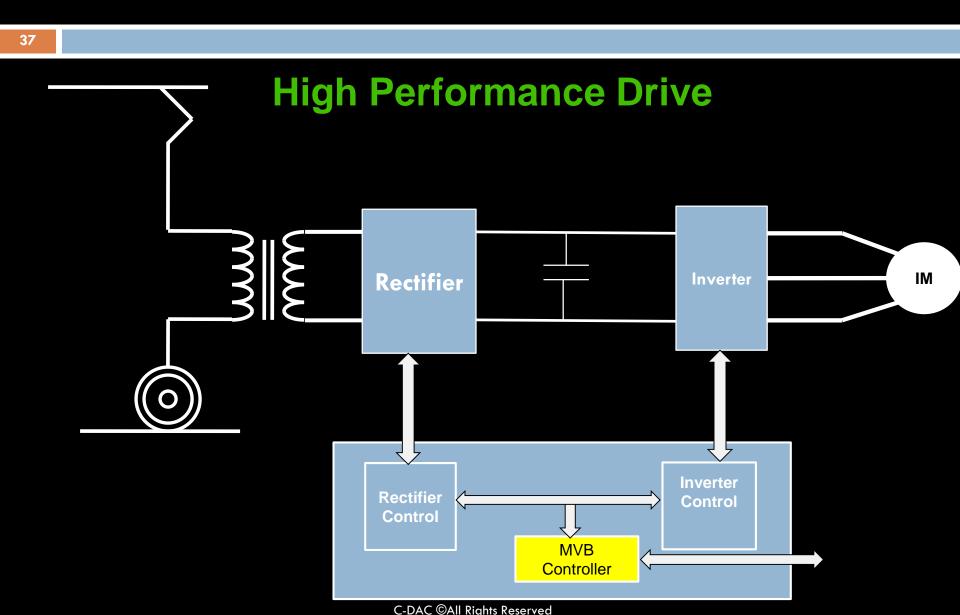

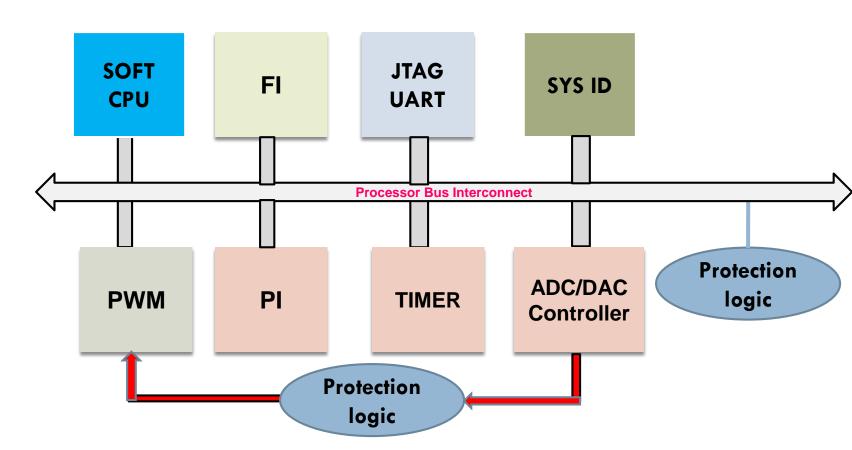

## **SOPC Configuration**

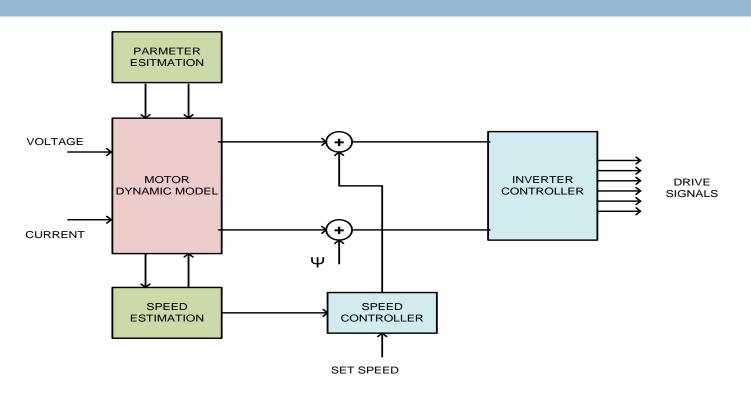

## **Inverter Control**

- □ Motor Model Estimates The speed from Voltage and currents

- DSP/Micro controller implementation, the motor model and other control blocks will be implemented as a software program.

- □ In SOPC architecture, control blocks are realized in Hardware using HDL called IPs

### **SOPC Configuration For Inverter Control**

39

Control blocks now part of the CPU – Hardware Modules

Other similar PE applications with out redesign -"Reuse"

Can be accessed Using Custom Instructions/Functions

### **IPs Required for The application**

| 1 | n |  |

|---|---|--|

|   | 9 |  |

| SOPC Configuration for <b>DC-DC</b> | SOPC Configuration for |  |

|-------------------------------------|------------------------|--|

| Control                             | Inverter Control       |  |

| IP cores for Basic control          |                        |  |

| Soft Processor core                 | Soft Processor core    |  |

| PI Controller                       | PI Controller          |  |

| PWM(2 Channel)                      | Motor Dynamic Model    |  |

| Subtraction                         | PWM(6 Channel)         |  |

| Limiter                             | Phase Transformers     |  |

Multi processor core Implementation in one FPGA Possible

## **Processors in FPGAs**

## Soft or Hard CPU cores

### Soft Processor

- Processor implemented in VHDL, Verilog, etc., and downloaded onto FPGA hardware

- > Example: NIOS II, MicroBlaze, ARM Cortex-M1 etc

- > Highly Reconfigurable ,a schematic (or code like software).

"More than 20 soft core processors are available" LEON 3, S1 core (64 Bit), ARM Cortex –M1,DSPUVA-16 etc

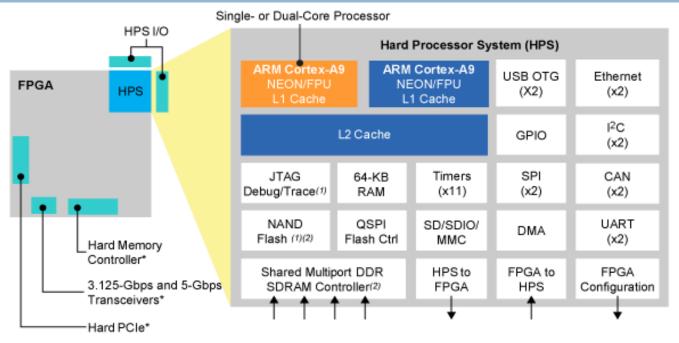

## Hard processors on FPGA

42

\*Optional Configuration

SoC FPGA

FPGA + Hard Processor System (HPS)

Can't alter Placement , Routing, and Area

Cyclone V SoC from Altera

Optimized for Higher speed of operation 925 MHz

Costly

## ALTERA NIOS II CPU

#### 43

- Full 32-bit instruction set, data path, and address space

- 32 external interrupt sources

- Single-instruction 32 x32 multiply and divide producing a 32-bit result.

- Access to a variety of on-chip peripherals, and interfaces to off-chip memories and peripherals

- Speed : 20 MHz to 430 MHz

44

□The top level entity of the IPs should meet AVALON Specification for NIOS□For ARM, AMBA Bus specification

- The Control blocks should be designed in HDL

- Functionality and timing are properly monitored using test bench or IP Verification methods.

- Time consuming process but one time process

# **Technology Developed**

- PE IP Library

- PE Specific IPs

- Design procedure for the IP Developer

- Drivers for PE IP library

- Design procedure for SOPC user

- SOPC Controller Card

- SOPC Interface Card

- PE Application Evaluation Report

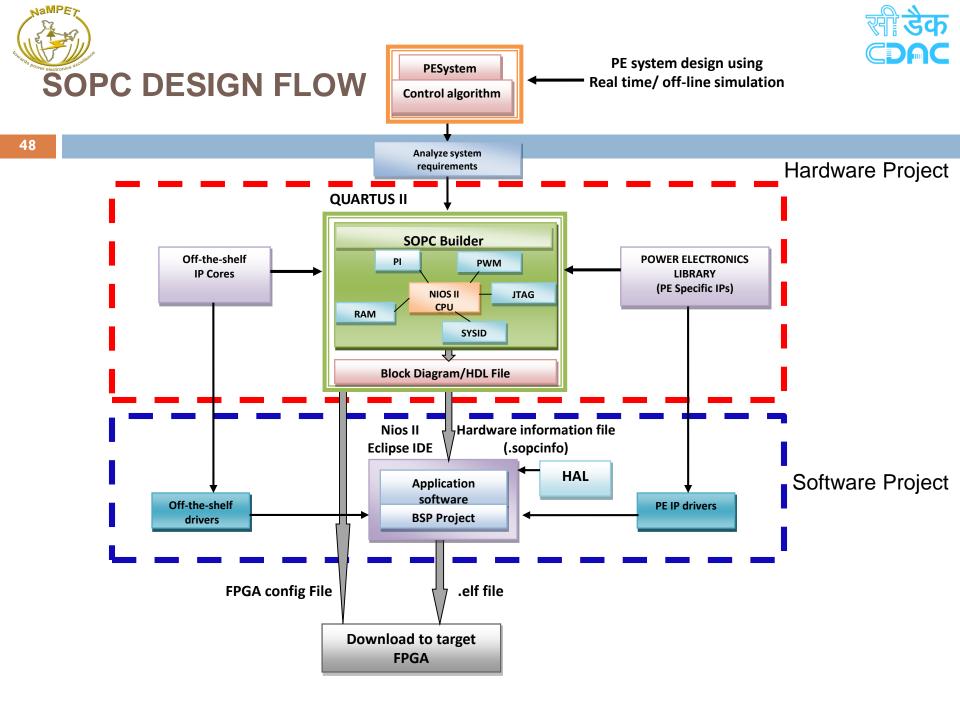

- Tools

- Altera QUARTUS II V9.1 or higher with SOPC Builder/Qsys

- NIOS II Eclipse IDE for software development

- Model sim for Simulation

- Hardware

- SOPC\_PE CONTROLLER\_V1 card SOPC Peripheral Board

49

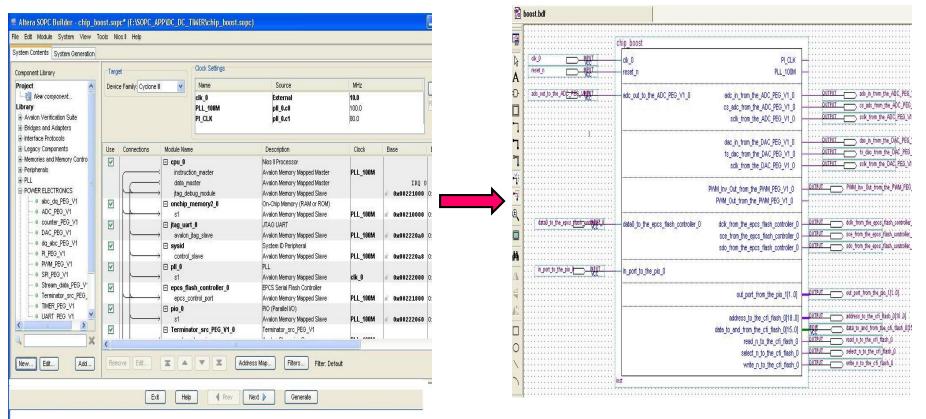

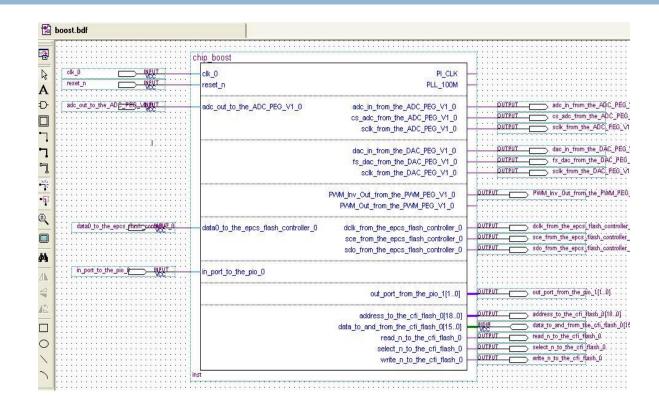

#### □ Drag and drop approach

#### ALTERA SOPC Builder /Qsys

#### Processor (Block view)

For Xilinx - Vivado

### **Application Software Design**

### NIOS II Eclipse IDE – NIOS II EDS

Supports Assembly, C/C++

### HAL/MicroC/OS II

> HAL

- Confirming POSIX Standards

- Vendor Altera

BSP is generated from '.sopcinfo' file and loads the required drivers from library

## **Custom instructions/Custom functions**

- Control blocks are accessed through custom instructions/custom functions

- Fixed Instruction

- > Simple and easily understandable by the user

For the PI Controller

> initialize PI module with Kp and Ki Registers

hw\_init\_pi(PI\_PEG\_V1\_0\_BASE, Kp\_val ,Ki\_val);

> enable/disable PI Module

hw\_enable\_pi(PI\_PEG\_V1\_0\_BASE,PI\_Cntrl\_Reg);

> input to the PI module

hw\_pi\_in(PI\_PEG\_V1\_0\_BASE,error);

> out from the PI module

pwm\_input= hw\_pi\_read\_output(PI\_PEG\_V1\_0\_BASE);

- Good Readability

- Number of lines are less

- Faster execution

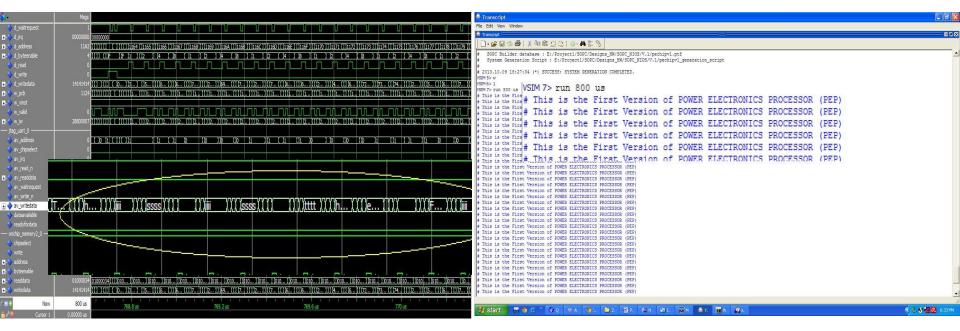

### **SOPC** Simulation

53

### Using ModelSim

# Can verify SOPC Hardware and application software together - Hardware Software - Co verification

Hardware Signal Flow

JTAG terminal

## **Technology Deliverables**

**SOPC PE Controller**

- Soft processor Integrated controller design procedure and user manual

- HDL control library elements for hardware accelerators (PI controller, Filters, PLL, PWM, Phase Transformations etc)

#### > 19 PE Specific IPs

- Application evaluation report using SOPC standard (v1.0) controller

- Voltage Mode control of DC-DC Boost converter

- AC drive –VVVF AC Induction Motor Single core and Multi core

- FOC of Induction Motor (As HiL in FSS miniature)

#### www.nampet.in

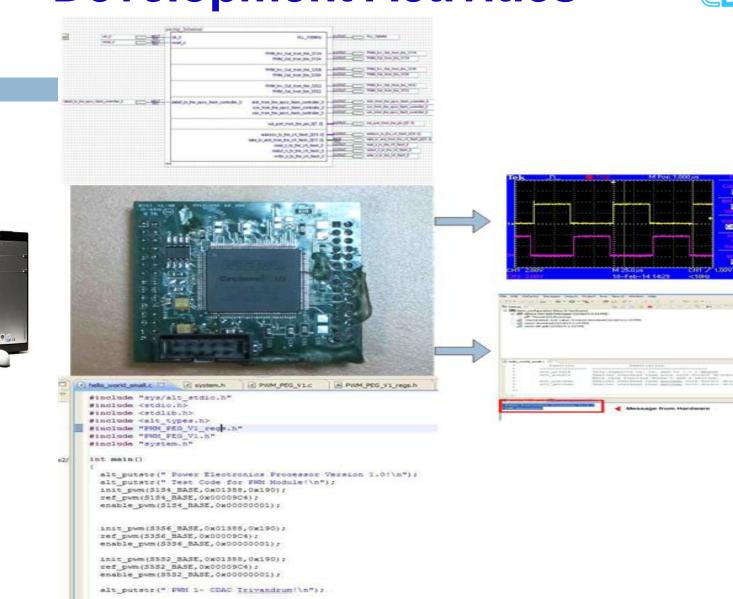

# **Development Activities**

जी के मिल

205 200

044

/\* Event loop never exits. \*/

Problems 💭 Tasks 📴 Console 💠 🛄 Properties

while (1);

No consoles to display at this time.

## ि SOPC Configured for Dc-Dc Control

57

PI controller is a Hardware module to the CPU

Accessed by custom functions

eg:- pi\_in(PI\_PEG\_V1\_0\_BASE,error);

pwm\_input = pi\_read\_output(PI\_PEG\_V1\_0\_BASE);

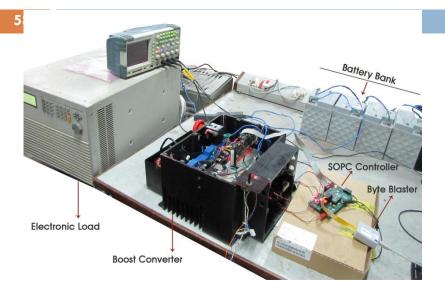

## **DC-DC Converter control**

#### Test setup of DC-DC Converter

#### **Bench Marking**

| Application | TMS320F2812     | SOPC           |

|-------------|-----------------|----------------|

| Boost       | 6 μs(CPU clock- | 800 ns(CPU     |

| Converter   | 150 MHz)        | clock-100 MHz) |

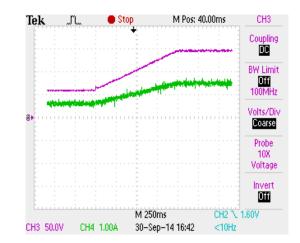

#### Output voltage(pink) and load current(green) during softstart

Inductor current (green) and PWM Pulse (blue) in steady state

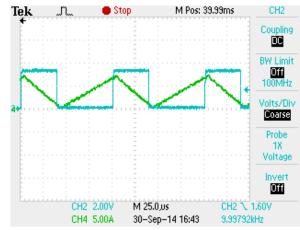

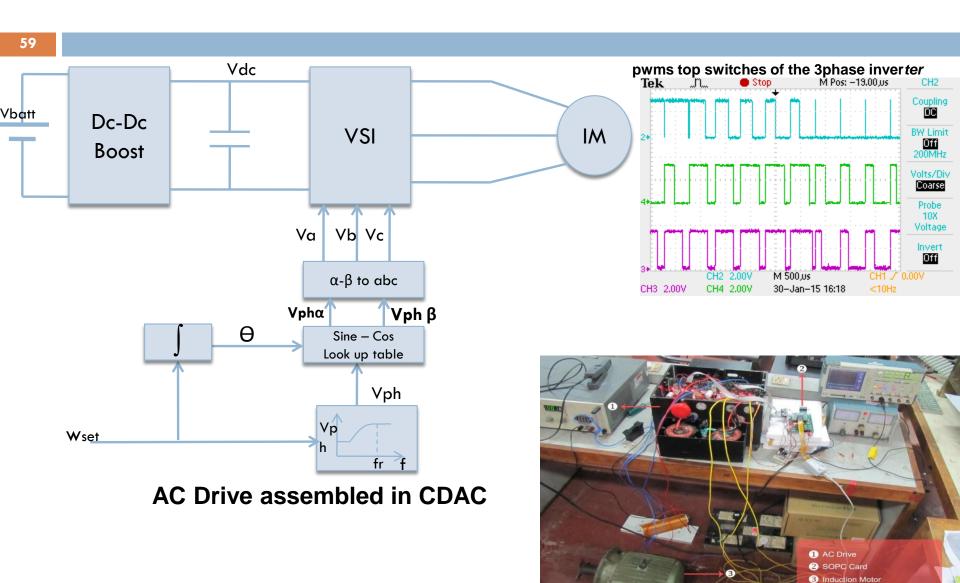

#### **AC Drive control**

# **AC Drive control**

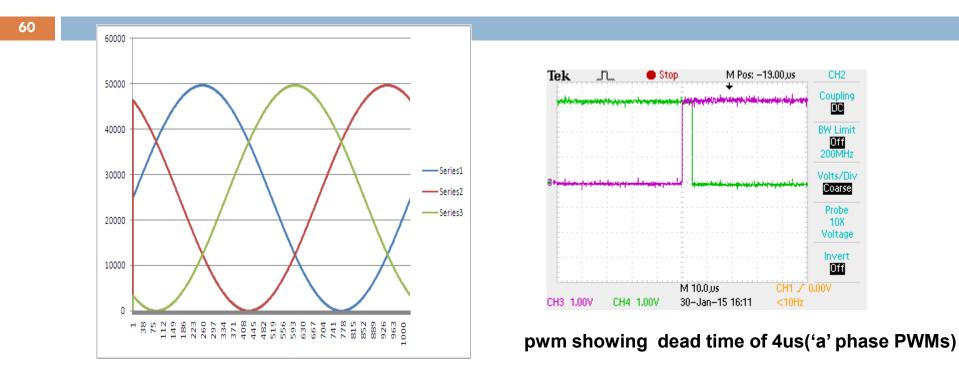

# Plot of Va, Vb and Vc values from NiosII through alpha\_beta\_abc IP

$\alpha$ - $\beta$  to abc, Integrator are in Hardware The C code implementation of  $\alpha$ - $\beta$  to abc, took - 600ns alpha\_beta \_to\_abc IP took only 300ns to perform the conversion

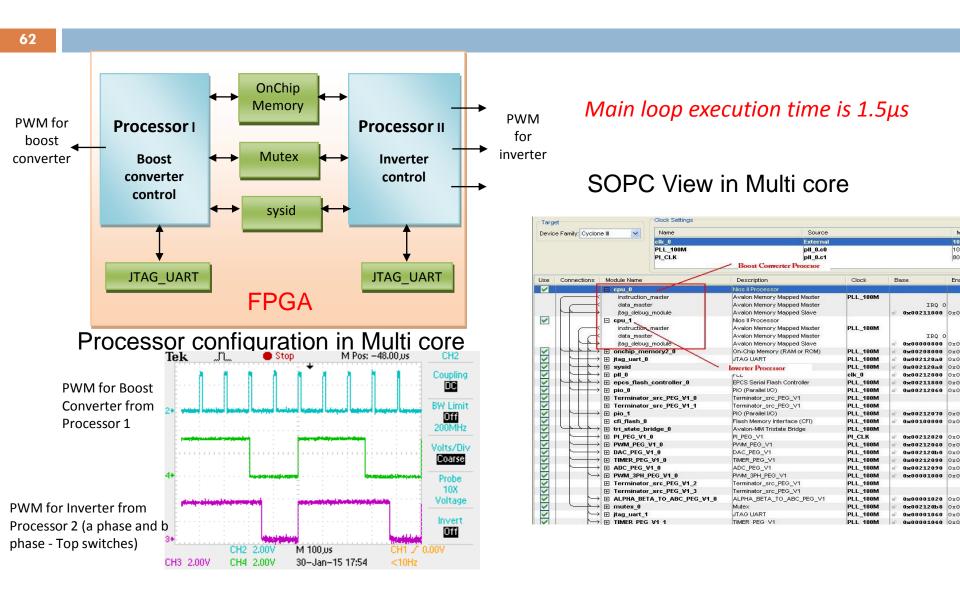

#### Main loop execution time = 2 us

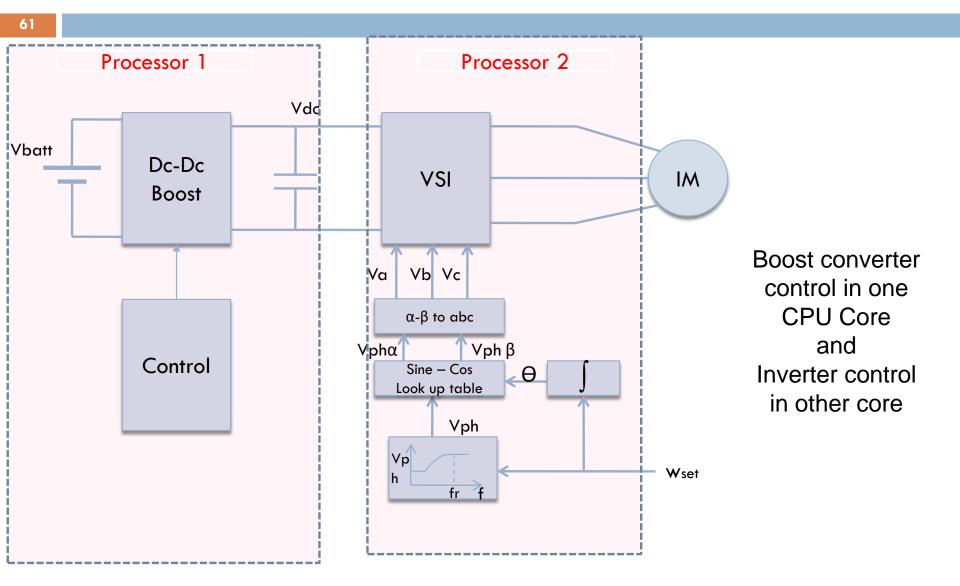

# AC Drive application in Multi-core

सी डैक CDAC

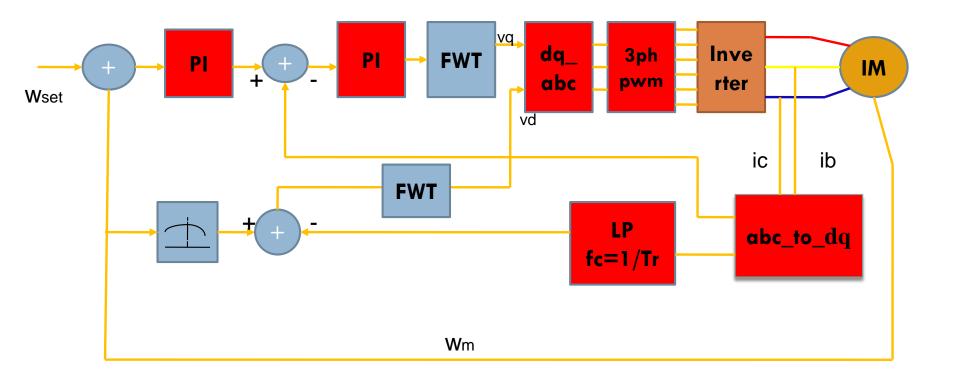

### FOC on SOPC

Red blocks – are hardware IPs

Main loop execution = 10 us in 100MHz For TMS 320F2814 = 22 us in 150MHz

### **Design flow**

64

#### Off the Shelf CPU Cores -NIOS II, Mico Blaze, Leon3 etc.

65

### **Design flow**

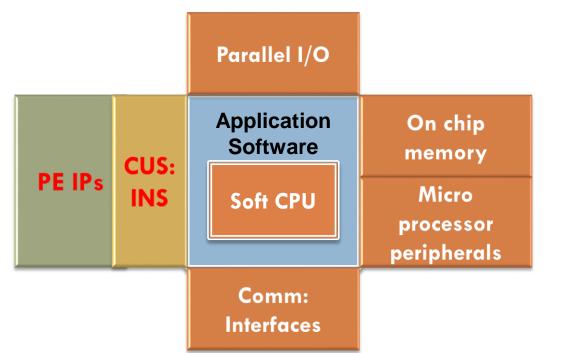

Parallel I/OSoft CPUOn chip<br/>memoryMicro<br/>processor<br/>peripheralsComm:<br/>Interfaces

Micro processor peripherals :- JTAG, Hardware Multiplier, memory interfaces, sys\_id etc. Communication Interfaces :- CAN,USB etc.

### **Design flow**

66

|        | Parallel I/O        |                                   |

|--------|---------------------|-----------------------------------|

| PE IPs | Soft CPU            | On chip<br>memory                 |

|        |                     | Micro<br>processor<br>peripherals |

|        | Comm:<br>Interfaces |                                   |

#### PE IPs :PWM ,PI,abc\_to\_dq,dq\_abc, ADC/DAC controllers,Integrators etc.

### **Design flow**

67

For Multiplication - MUL A,B Similarly For PI Controller IP hw\_pi\_in(PI\_ID,error); out = hw\_pi\_read(PI\_ID);

Number of lines in the application code is less

C-DAC @All Rights Reserved

# Soft IP core: Design Advantages

69 SOPC PE Controller

- Higher level of design reuse

- Re-configurability

- Reduced obsolescence risk

- Simplified design update or change

Lesser over head in control software design

- Parallel Processing

- Improved Time to market

- Single to multi-core flexibility

# **THANK YOU**

ajeesh@cdac.in